99 South Street Hopkinton, MA 01748 (617) 435-5395 Telex: 298281

Q-RAM 88B

USER INFORMATION MANUAL

If my memory serves me right . . . it must be Clearpoint.

### TABLE OF CONTENTS

| CHAPTER 1 - GENERAL | DESCRIPTION | AND | SPECIFICATIONS |

|---------------------|-------------|-----|----------------|

|---------------------|-------------|-----|----------------|

| 1.1   | Introduction1-1                                        |

|-------|--------------------------------------------------------|

| 1.2   | General Description1-2                                 |

| 1.3   | Backplane Pin Utilization1-4                           |

| 1.4   | Specifications1-6                                      |

| СНАРТ | ER 2 - HARDWARE INSPECTION, INSTALLATION, AND CHECKOUT |

|       | Hope infor, MA-D1748                                   |

| 2.1   | Introduction2-1                                        |

| 2.2   | Configuring the Q-RAM 88B Program Plugs2-1             |

| 2.3   | Addressing Options2-1                                  |

| 2.4   | Board Size Configuration Plugs2-3                      |

| 2.5   | CSR Option Plug Configurations2-3                      |

| 2.6   | Battery Backup Option Plugs2-4                         |

| 2.7   | Installation Procedure2-5                              |

| CHAPT | ER 3 - CSR DESCRIPTION                                 |

| 3.1   | Introduction3-1                                        |

| 3.2   | CSR Bit Assignment3-1                                  |

| FIGUR | ES                                                     |

| Figur |                                                        |

| Figur | e 2 Q-RAM 88B1-3                                       |

|       |                                                        |

### TABLES

|            | •                                               |

|------------|-------------------------------------------------|

| Table 1    | Q-RAM 88B Products1-1                           |

|            |                                                 |

| Table 2    | Backplane Power Pins1-4                         |

| Table 3    | Backplane I/O Signal Pins1-5                    |

| Table 4    | Multiple Q-RAM 88B Starting Addresses2-2        |

| Table 5    | Memory Size Jumpers2-3                          |

| Table 6    | CSR Address Selection2-4                        |

| Table 7    | Battery Backup Mode Options2-4                  |

| Table 8    | CSR Bits 5 to 113-3                             |

|            | nereafter retained to as DACA: Q-808. 256R      |

| APPENDIXE  | asad as individual storage devices to provide C |

|            |                                                 |

| Appendix   | 2 4 7 章 · 从外是                                   |

| Appendix   |                                                 |

| Appendix   | C Bank Select Instruction                       |

|            | - Jupper selectible 18 u. 17 nit no             |

|            | - Parity generation and oher ing on             |

|            | - Copplete DEC softward-hardware                |

|            | parity control and status regist                |

|            | incatable at any of 6 sesigned 1-0.             |

|            |                                                 |

|            | - Stagle 5 volt power supply                    |

|            | ts lidsomolpoiq asdiess proties -               |

|            |                                                 |

| noifseibn. |                                                 |

|            |                                                 |

|            |                                                 |

|            |                                                 |

### CHAPTER 1

### GENERAL DESCRIPTION AND SPECIFICATIONS

# 1.1 INTRODUCTION

This manual supplies user information for the Q-RAM 88B family of memory modules. Q-RAM 88B modules (see Table 1) provide high density, low cost per bit storage for systems which utilize the Digital Equipment Corporation (hereafter referred to as DEC\*) Q-BUS. 256K MOS RAMS are used as individual storage devices to provide up to 4 mbyte on a single quad-height board. Features available on Q-RAM 88B are:

- Up to 4 MB memory capacity

- Jumper selectable 18 or 22 bit addressing

- Parity generation and checking on board

- Complete DEC software-hardware compatible, parity control and status register on board locatable at any of 8 assigned I/O page address

- Battery back-up support

- Single 5 volt power supply

- Starting address programmable at any 256K boundary

- Parity error LED provides visual indication of board failure

# Table-1 Q-RAM Products

| Design |       | scription |    |       |

|--------|-------|-----------|----|-------|

| Q-RAM  | 88B   | 4         | MB | board |

| Q-RAM  | 88B-2 | 2         | MB | board |

<sup>\*</sup>Registered trademark of Digital Equipment Corporation

### 1.2 GENERAL DESCRIPTION

The Q-RAM 88B is a single quad-height memory module which interfaces to the LSI-ll Q-BUS. All timing and control logic for the memory, refresh circuitry, parity control, and status register are contained on board.

The MOS memory array consists of up to eight rows of 262,144 X 1 bit dynamic RAM devices with 18 devices per row. Each row will accept 262,144 18 bit words consisting of (two) eight bit bytes and two parity bits (one per byte). Circuitry for refresh of the MOS memory devices is provided on board and operates transparently to the user.

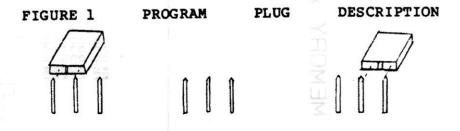

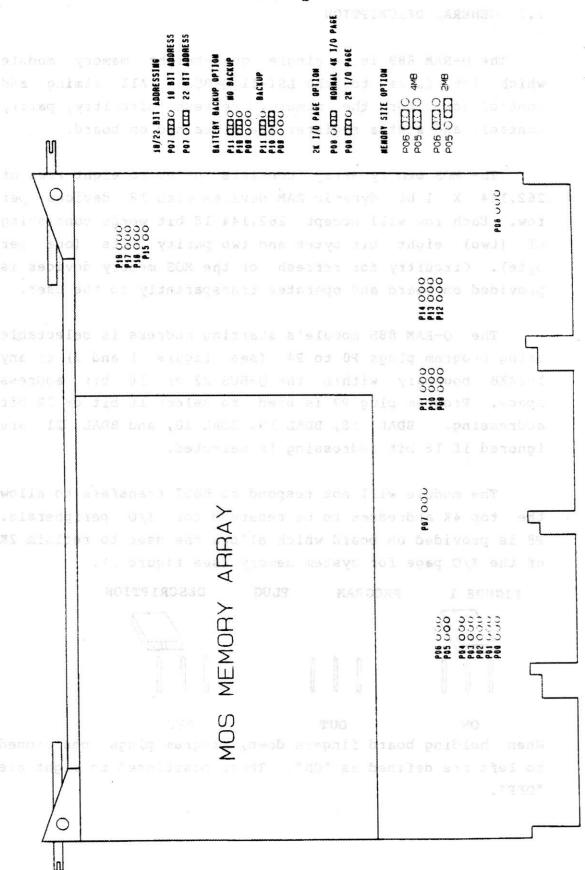

The Q-RAM 88B module's starting address is selectable using program plugs PO to P4 (see figure 1 and 2) to any 1024KB boundary within the Q-BUS 22 or 18 bit address space. Program plug P7 is used to select 18 bit or 22 bit addressing. BDAL 18, BDAL 19, BDAL 20, and BDAL 21 are ignored if 18 bit addressing is selected.

The module will not respond to BBS7 transfers to allow the top 4K addresses to be reserved for I/O peripherals. P8 is provided on board which allows the user to reclaim 2K of the I/O page for system memory (see figure 2).

OUT

ON

When holding board fingers down, program plugs positioned to left are defined as "ON". Those positioned to right are "OFF".

OFF

When any byte of data is written to Q-RAM 88B boards which contain parity, a parity bit is generated which is stored along with the byte of data in the memory array. Whenever a byte of data is read the parity logic checks it against the stored parity bit. If parity is bad, an error has occurred and data is assumed to be bad.

In order to utilize the parity generation and checking circuitry in the Q-RAM 88B, a control and status register is provided on board which is both hardware and software compatible with LSI-ll systems.

The control and status register is used to enable the board to interrupt if an error has occurred, latch the upper address bits of the location with bad data, set the parity error flag on error, and force bad parity writing for diagnostic purposes.

### 1.3 BACKPLANE PIN UTILIZATION

Table 2 contains backplane power pins required for Q-RAM 88B. Table 3 designates pins used for other signals. Board finger designations shown in figure 2 are equivalent to backplane pin designations.

Table-2 Backplane Power Pins Required

| Voltage Lage               | $niq_{BK2}$ |

|----------------------------|-------------|

| +5 normal                  | BVl         |

|                            | SMS AA2     |

| J 60 JAJ8                  | BA2         |

| ground                     | LTABP2      |

| J EF LAGE                  | SABEL       |

| BDAL 12 E                  | Sag AC2     |

|                            | BC2         |

| J & J LAGE                 |             |

| +5 battery (if used)       | AVI         |

| +5 Battery spare (if used) | AS1         |

|                            | AEl         |

|                            | AE.         |

|           | Signal  |          |           |           | Pin    |                      |   |

|-----------|---------|----------|-----------|-----------|--------|----------------------|---|

|           | ACI     | sc od: 1 |           |           | ממעט   |                      |   |

|           | AD1     |          |           |           | BDAL   | 17                   | L |

|           | BAl     |          |           | date in   | BDCOK  | H                    |   |

|           | BC1     |          |           |           | BDAL   | 18                   | L |

| checking  | BD1     |          |           |           | BDAL   | 19                   | L |

|           | BEL     |          | 5 .888    |           | BDAL   | 20                   | L |

|           | BF1     | hoth     | si dose   |           | BDAL   | 21                   | L |

|           | AE2     |          | ejastens. |           | BDOUT  | $\mathbf{L}^{\perp}$ |   |

|           | AF2     |          |           |           | BRPLY  | L                    |   |

|           | AH2     |          |           | and 'F'   | BDIN   | L                    |   |

|           | AJ Z    |          |           |           | DUTING |                      |   |

|           | AK2     |          |           |           |        |                      |   |

|           | AM2     |          | ,1011     |           | BIAKI  | L                    |   |

|           | AN2     |          |           | 11 202 21 | BIAKO  | L                    |   |

|           | AP2     |          |           |           | BBS7   | L                    |   |

|           | AR2     |          |           |           | BDMG I | L                    |   |

|           | AS2     |          |           |           | BSMG   | L                    |   |

|           | AU2     |          |           |           | DUAL   | 00                   | L |

|           | AV 2    |          |           |           | DUAL   | 01                   | L |

| quivalent | BE2     | it at a  |           |           | DUAL   | 02                   | L |

|           | BF2     |          |           |           | BDAL   | 03                   | L |

|           | вн2     |          |           |           | BDAL   |                      |   |

|           | вј2     |          |           | Plane P   | BDAL   | 05                   | L |

|           | BK2     |          |           |           | BDAL   | 06                   | L |

|           | BL2     |          |           |           | BDAL   | 07                   | L |

|           | BM2     |          |           |           | BDAL   | 8 0                  | L |

|           | BN2     |          |           |           | BDAL   | 09                   | L |

|           | BP2     |          |           |           | BDAL   | 10                   | L |

|           | BR2     |          |           |           | BDAL   | 11                   | L |

|           | BS2     |          |           |           | BDAL   | 12                   | L |

|           | SD8 BT2 |          |           |           | BDAL   | 13                   | L |

|           | BU2     |          |           |           | BDAL   |                      |   |

|           | IVA BV2 |          |           |           | BDAL   | 15                   | L |

### 1.4 SPECIFICATIONS

SPECIFICATIONS CHARACTERISTICS MOS dynamic RAM memory device type (262,144 X 1) read access time 200 ns typ. 50 ns typ. write access time 450 typ. memory cycle time 0 to +65 C operating temperature storage temperature -40 to +85 C 0 to 90% (non-condensing relative humidity +5V +5% pins BUl, AA2, BA2 voltages required +5V +5% pins AV1, AS1\*, AE battery backup voltage +5V operating current 2 amp max. +5V standby current 1.9 amp max. +5V battery backup current .9 amp max. iqure I provides the locations of the various Q-RAM

\* optional spares available on backplane

2-RAM 88B addressing logic is capable of either 22 or 8 oit operation. P7 is used to select the desired odressing mode as follows:

P7 - ON 18 Bit Address Mode P7 - OFF 22 Bit Address Mode

BDAL 18, BDAL 19, BDAL 20, and BDAL 24 are ignored if 18 bit addressing mode is selected and the board key not be continued to respond to addresses above 128K.

The memory starting address may be programmed at any 1024KR boundary using jumpers PR thru P4. Depending on the size of the board, the memory will utilize up to 2.097,152 contiquous word addresses in the address space beginning at

### CHAPTER 2

# HARDWARE INSPECTION, INSTALLATION, AND CHECKOUT

### 2.1 INTRODUCTION

This chapter provides information for configuring the Q-RAM 88B programmable plug options prior to system installation followed by installation and checkout procedures.

# 2.2 CONFIGURING THE Q-RAM 88B PROGRAM PLUGS

Figure 2 provides the locations of the various Q-RAM 88B option jumpers and Figure 1 illustrates how they are used. The module should be inspected prior to installation to assure that it has been properly configured. Sections 2.3 through 2.6 describe the various Q-RAM 88B program plug options.

### 2.3 ADDRESSING OPTIONS

Q-RAM 88B addressing logic is capable of either 22 or 18 bit operation. P7 is used to select the desired addressing mode as follows:

P7 - ON

18 Bit Address Mode

P7 - OFF

22 Bit Address Mode

BDAL 18, BDAL 19, BDAL 20, and BDAL 21 are ignored if 18 bit addressing mode is selected and the board may not be configured to respond to addresses above 128K.

The memory starting address may be programmed at any 1024KB boundary using jumpers P0 thru P4. Depending on the size of the board, the memory will utilize up to 2,097,152 contiguous word addresses in the address space beginning at

the selected starting address. Q-RAM 88B board size options are described in section 2-4.

To program the starting address of memory, BDAL 21 through BDAL 17 must be reflected by the following program plug configurations:

| BDA | AL 2 | 21 | 1         |           | P4 | 2.4 BOARD SIZE COMPLEMO  |

|-----|------|----|-----------|-----------|----|--------------------------|

| BDA |      |    |           |           |    | OFF                      |

| BDA | AL 2 | 20 | 1 intiged |           | P3 | sluge PS and P6 ano      |

| BDA | AL 2 | 20 | ows of 0  |           |    | OFF van abisod 888 MAR-O |

| BDA | AL I | 19 | 101 Teg   | devices   | P2 | dynamic RAM devices w NO |

| BDA | AL I | 19 | 0 -0 A    |           | P2 | accept 262,144 (256K)770 |

| BDA | AL : | 18 | 1001100   |           |    | 2, 4, or 8 rows of MO    |

| BDA | AL : | 18 | 0 24 "A   | pectively | P1 | 1024K, of 2048K wordan   |

| BDA | AL : | 17 | to match  |           | P0 | configured, as shown ino |

| BDA | AL : | 17 | 0         |           | P0 | off bear on board        |

|     |      |    |           |           |    |                          |

Appendix A may be used to determine starting addresses if the Q-RAM 88B is to placed over existing resident memory. Table 4 may be used as an illustration of the above described formula. Table 4 may also be used to directly configure systems with multiple Q-RAM 88B 1 MB boards.

Table-4 Multiple Q-RAM 88B Starting Addresses

| BRD       |     | ST  | ARTI | NG A | DDRE | SS  |      |         | P           | LU | G CO | NFIGI | JRAT | IONS |

|-----------|-----|-----|------|------|------|-----|------|---------|-------------|----|------|-------|------|------|

| (herea    | A21 | A20 | A19  | A18  | A17  | A16 | A15  | rity c  | sg <b>e</b> | 4  | P3   | P2    | Pl   | P0   |

| the 1     | 0   | 0   | 0    | 0    | 0    | 0   | 0    |         | O           | FF | OFF  | OFF   | OFF  | OFF  |

| 2         | 0   | 1   | 0    | 0    | 0    | 0   | 9 10 | This a  | C           | FF | ON   | OFF   | OFF  | OFF  |

| 3 38 1901 | 1   | 0   | 0    | 0    | 0    | 0   | 0    |         | C           | N  | OFF  | OFF   | OFF  | OFF  |

| 9647 96   | 10  | °f° | 0    | 0    | 0    | 0   | 0    | and Pla | E           | N  | ON   | OFF   | OFF  | OFF  |

The BBS7 signal is used during the address portion of a data transfer cycle on the Q-BUS. It indicates that the bus master is requesting a data transfer with one of the I/O devices in the 4K I/O page space. BBS7 is asserted whenever an I/O page transfer is requested. The memory board should ignore all transfers requested within the I/O

space. If, however, there are few peripherals on the system and it is desired by the user to reserve only 2K of the I/O page space, plug P8 may be used as follow:

P8 - OFF Normal 4K I/O Page

P8 - ON Reserve Only 2K I/O Page

### 2.4 BOARD SIZE CONFIGURATION PLUGS

Plugs P5 and P6 are used to configure the board size. Q-RAM 88B boards have up to eight rows of 262,144 X l bit dynamic RAM devices with 18 devices per row. Each row will accept 262,144 (256K) 18 bit words. A Q-RAM 88B may have 2, 4, or 8 rows of memory chips corresponding to 512K, 1024K, or 2048K words respectively. P5 and P6 must be configured, as shown in Table 5, to match the size of the memory array on board.

Table-5 Memory Size Jumpers

|         | Board memory capacity | P5  | P6  |

|---------|-----------------------|-----|-----|

|         | 512K words (1 MB)     | OFF | OFF |

| od best | 1024K words (2 MB)    | OFF | ON  |

|         | 2048K words (4 MB)    | ON  | ON  |

# 2.5 CSR OPTION PLUG CONFIGURATION

The parity control and status register (hereafter referred to as CSR) has an I/O page address in the top 4K of memory. This address may be any one of eight specified locations reserved by DEC for this purpose. Program plugs Pl2, Pl3, and Pl4 are used to select one of the reserved addresses. Table 6 illustrates the use of these plugs. Note that each memory board used in a system must be configured to a different address.

Table-6 CSR Address Selection

| CSR Address       | P14 | P13          | P12 |

|-------------------|-----|--------------|-----|

| 772100            | ON  | ON           | ON  |

| 772102            | ON  | ON POLICE SE | OFF |

| 772104            | ON  | OFF          | ON  |

| 772106            | ON  | OFF          | OFF |

| 772110            | OFF | NO Visually  | ON  |

|                   | OFF | ON           | OFF |

| 772114            | OFF | OFF          | ON  |

| 772116            | OFF | OFF          | OFF |

| No CSR or Parity* | OUT | OUT          | OUT |

\*To disable parity, remove Pl2, Pl3, and Pl4 plugs

3. Verify that the required power connections are

# 2.6 BATTERY BACKUP OPTION PLUGS

The MOS memory, unlike core memory, requires the 5 volt supply to retain data. If the 5V power is removed from the board, system memory data is lost.

The battery backup option is used if battery power is available to maintain system memory data during power failures. Battery backup 5V must be available on backplane pin AVI. ASI or AEI may be used as an additional battery backup 5V input pin. Table 7 shows the various configurations of the battery backup mode select plugs P9, P10, and P11.

Table-7 Battery Backup Mode Options

6. Power up the system and run any DBC memory

diagnostic as an initial test. if available, use

| Battery Backup Mode        | P11 | P10 | <u>P9</u> |

|----------------------------|-----|-----|-----------|

| No Backup                  | ON  | ON  | OUT       |

| Battery Backup +5 AV1      | OFF | OFF | OUT       |

| (AS1, AE1 unused)          |     |     |           |

| Battery Backup +5 AV1,AS1  | OFF | OFF | ON        |

| Battery Backup +5 AV1, AE1 | OFF | OFF | OFF       |

### 2.7 INSTALLATION PROCEDURE

The following procedure should be followed when a CLEARPOINT MEMORY board is received:

Visually inspect the module to make sure that it has arrived in good condition.

J 7 2 2 1 8 6

- Set up program plug options for required operation.

- Verify that the required power connections are available on the backplane (see Table 2).

- 4. Power down the system. Make sure that the system is powered off before plugging in a module.

- 5. Plug the module into the Q-BUS. Some DEC literature suggests that memories be installed in sequential slots following the CPU. However anyplace in the backplane is sufficient. Do make sure that the module is not being inserted backwards; the component side must face in the same direction as other modules in the system.

- 6. Power up the system and run any DEC memory diagnostic as an initial test. If available, use the following diagnostics.

MAINDEC-11 CVMSA (22 bit system diagnostic)

MAINDEC-11 CZKMA (18 bit system diagnostic)

## CHAPTER 3

### CSR DESCRIPTION

### 3.1 INTRODUCTION

When any byte is written to Q-RAM 88B boards with parity option, a parity bit is generated which is stored along with the byte of data in the memory array. Whenever a byte of data is read, the parity logic checks it against the stored parity bit. If parity is bad, an error has occurred and data is assumed to be bad.

In order for software to utilize the parity generation and checking circuitry in the Q-RAM 88B, a control and status register (CSR) is provided.

The CSR is assigned an address in the I/O page (see Table 6) which may be accessed by software. When a parity error is detected, the upper address bits of the bad memory location (All to A21) are latched in the CSR. Control bits are provided in the CSR to enable interrupt on error and write of bad parity for diagnostic purposes.

### 3.2 CSR BIT ASSIGNMENT

The CSR is a 16 bit register located in the I/O page. The function of the 16 bits in the CSR are as follows:

# Bit 0 Parity error interrupt enable

If set to 1, the memory board will interrupt the processor on error, by setting bits BDAL 17 and BDAL 16 along with the data bits BDAL 0 to BDAL 15.

This will result in an LSI-11 processor trap to location 114. BUS INIT clears this bit.

Bit 1 UNUSED

Bit 2 Write wrong parity

If this bit is set to 1, any word or byte written to the array will be stored along with an incorrect parity bit. This is for maintenance purposes. It enables didagnostics to check the boards ability to detect parity errors and interrupt when enabled. This bit is cleared by BUS INIT.

Bit 3 UNUSED

Bit 4 UNUSED

Bit 5 - 11 Latch address bits

When a parity error is detected, the upper address bits of the failing location are latched. These bits are not cleared by BUS INIT, but are writeable, as well as readable. When an error is detected, address bits ll to 21 are displayed in these bits. Since there are only 7 bits and there are 11 latched address bits, they are multiplexed. Bit 14 in the CSR controls which of the latched address bits are on display. (see Table 8).

Bit 12 UNUSED

Bit 13 UNUSED

Bit 14 Extended CSR read enable

(See Table 8.) This bit is used to multiplex the extended latched address bits Al8 to A21 into the CSR bits 5 to 11. This bit is cleared by BUS INIT. Program plug P17 may be used to disable setting of bit 14. If plug P17 is on, CSR bit 14 is always 0.

## Bit 15 Parity error flag

This bit is set if a parity error is detected and remains set until cleared by being written or by BUS INIT.

Table-8 CSR Bits 5 to 11

| CSR Bit | If CSR Bit 14-0 | If CSR Bit 14-1 |

|---------|-----------------|-----------------|

| 05      | Latched All     | Latched Al8     |

| 06      | Latched Al2     | Latched Al9     |

| 07      | Latched Al3     | Latched A20     |

| 08      | Latched Al4     | Latched A21     |

| 09      | Latched Al5     | 0               |

| 10      | Latched Al6     | 0               |

| 11      | Latched Al7     | 0               |

APPENDIX A

## · MEMORY STARTING ADDRESS CHART

| Resident memory |      | St  | arti         | ng A | ddre | SS  |  |

|-----------------|------|-----|--------------|------|------|-----|--|

| in K words      |      | A21 | A20          | A19  | A18  | A17 |  |

| 0 K             |      | 0   | 0            | 0    | 0    | 0   |  |

| 6 4 K           |      | 0   | 0            | 0    | 0    | 1   |  |

| 128K (1/4 MB)   |      | 0   | 0            | 0    | 1    | 0   |  |

| 192K            |      | 0   | 0            | 0    | 1    | 1   |  |

| 256K (1/2 MB)   |      | 0   | 0            | 1    | 0    | 0   |  |

| 320K            |      | 0   | 0            | 1    | 0    | 1   |  |

| 384K (3/4 MB)   |      | 0   | 0            | 1    | 1.   | 0   |  |

| 448K            |      | 0   | 0            | 1    | 1    | 1   |  |

| 512K (1 MB)     |      | 0   | - <b>1</b> - | 0    | 0    | 0   |  |

| 576K            |      | 0   | 1            | 0    | 0    | 1   |  |

| 640K (1 1/4 MB) |      | 0   | 3 <b>1</b> 1 | 0    | 1    | 0   |  |

| 704K            | 1.13 | 0   | 1            | 0    | 1    | 1   |  |

| 768K (1 1/2 MB) |      | 0   | 1            | 1    | 0    | 0   |  |

| 832K            |      | 0   | 1            | 1    | 0    | 1   |  |

| 896K (1 3/4 MB) |      | 0   | 1            | 1    | 1    | 0   |  |

| 960K            |      | 0   | 1            | 1    | 1    | 1   |  |

| 1024K (2 MB)    |      | 1   | 0            | 0    | 0    | 0   |  |

If starting address is greater than 2MB, subtract 2MB from the total. Set A21=1 and use table to determine state of A15 through A20 by finding remainder in table.

The Q-RAM 88B Block Mode DMA Memory Board

The Q-RAM 88B is designed to implement the block mode DMA protocols on the Q-BUS. Block Mode DMA reduces the "handshaking" necessary to transfer data and thereby increases the transfer rate by a factor of nearly 2. From the user's perspective there is no difference in the operation or configuration of the Q-RAM 88B since the board will operate transparently using whatever form of DMA is invoked by other devices on the bus.

# What is Block Mode DMA?

Under conventional direct memory access (DMA), direct data transfers between I/O devices and memory occur one (16 bit) word at a time or one byte at a time using DATI, DATO or DATO (B) bus cycles. Under block mode DMA, the starting address is followed not only by data for that address, but by data for up to 16 consecutive addresses. By eliminating the assertion of the address for each data word, the transfer rate is nearly doubled.

The Q-RAM 88B can also be used in system configurations with non-block mode DMA memory boards (either above or below). Most new Q-BUS peripheral controllers will be supporting block mode protocols and take advantage of the improved bus bandwidth using DATBI and DATBO type bus cycles. For devices already designed that do not use these block mode bus cycles, bus operation is unaffected.

For a complete technical description of these protocols, refer to the 1983 PDP-11 Micro/PDP-11 Handbook published by Digital Equipment Corporation.

### APPENDIX C

#### BANK SELECTION

The bank select feature designed into the Q-RAM 88B products is used essentially to increase the available main memory which is addressable in a Q-BUS\* system. With Clearpoint bank select memory, up to 32 megabytes may be used in a single Q-BUS system with no hardware modifications required.

To enable the Q-RAM 88B, bank selectability jumpers P15, P16, P17, and P18 (see figure 2) are used. If all of these jumpers are "out" (see figure 1), the bank select feature is disabled. To use this feature, P16, P17, and P18 must be installed. P15 may be installed as shown below (see table).

Any board which has jumpers P18, P17, and P16 installed will respond to writes (DOUT cycles) to I/O page CSR address 7775100 in one of the following two ways:

- If P15 is not installed, the board will latch bank select bits provided by D5,D6, and D7 in the word being written.

- 2. If P16,P17, and P18 are all on (see figure 1) and P15 is installed; the board will respond with BREPLY L to any write to address 177775100 and latch bank select bits from D5, D6, and D7 in the word being written.

Since 7775100 is a write only address the memory boards will not respond to read (DIN cycles) using 7775100 at all.

To verify data being written into bits 5, 6, and 7 of the bank select control status register, data written will be displayed in bits 5 - 11 of the parity control status register for each board.

\*Q-BUS is a registered trademark of Digital Equipment Corporation.

Bank selectable boards have unique parity CSR addresses as well. Boards which are not enabled for bank select have registers as described in Table 6. Parity CSR addressing for boards configured for bank select is described below.

Table 6 CSR Address Selection for Boards Enabled for Bank Select

| CSR Address   | P14      | P13 | P12 |

|---------------|----------|-----|-----|

| 772120        | ON       | ON  | ON  |

| 772120        | ON       | ON  | OFF |

| 772124        | ON       | OFF | ON  |

| 772126        | ON       | OFF | OFF |

| 772130        | OFF      | ON  | ON  |

| 772132        | OFF      | ON  | OFF |

| 772134        | OFF      | ON  | ON  |

| 772136        | OFF      | OFF | OFF |

| No CSR or Par | ity* OUT | OUT | OUT |

<sup>\*</sup>Parity may not be disables for bank selectable boards.

All memory boards in the system must have a unique parity CSR address. Parity must be enabled to use bank select.

The data bits written into CSR 7775100 bits 5, 6, and 7 select which page of memory will be accessible in bank selectable address space and up to eight pages may be available. The following table shows how jumpers P16, P17, and P18 correspond to the selection bits written into 7775100.

Table-7 Page Selection Options

| Bank Select | CSR   | CSR   | CSR   |     |     |     |

|-------------|-------|-------|-------|-----|-----|-----|

| Page        | Bit 7 | Bit 6 | Bit 5 | P18 | P17 | P16 |

| 0           | 0     | 0     | 0     | ON  | ON  | ON  |

| 1           | 0     | 0     | 1     | ON  | ON  | OFF |

| 2           | 0     | 1     | 0     | ON  | OFF | ON  |

| 3           | 0     | 1     | 1     | ON  | OFF | OFF |

| 4           | 1     | 0     | 0     | OFF | ON  | ON  |

| 5           | 1     | 0     | 1     | OFF | ON  | OFF |

| 6           | . 1   | 1     | 0     | OFF | OFF | ON  |

| 7           | 1     | 1     | 1     | OFF | OFF | OFF |